## System-on-chip design flow for Software Defined Radio Guangye Tian

### ▶ To cite this version:

Guangye Tian. System-on-chip design flow for Software Defined Radio. Other [cs.OH]. Université Paris Sud - Paris XI, 2011. English. NNT: 2011PA112099 . tel-00605989

## HAL Id: tel-00605989 https://theses.hal.science/tel-00605989

Submitted on 5 Jul 2011

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## THÈSE DE DOCTORAT

| '                                                    | SPECIALITE : INFORMATIQUE                      |  |  |  |

|------------------------------------------------------|------------------------------------------------|--|--|--|

| Ecole Doctorale « Informatique »                     |                                                |  |  |  |

| Présentée par :                                      | Mr. Guangye Tian                               |  |  |  |

| Sujet : Flot de Cone                                 | ception Système sur Puce pour Radio Logicielle |  |  |  |

| Soutenue le 28/06/2011 .devant les membres du jury : |                                                |  |  |  |

| MAlain MERIGOT, Président                            |                                                |  |  |  |

| M Guy GOGNIAT, Rapporteur                            |                                                |  |  |  |

| MSmail NIAR, Rapporteur                              |                                                |  |  |  |

| M Daniel ETIEMBLE, Directeur de thèse                |                                                |  |  |  |

M..... Omar HAMMAMI, Co-directeur de thèse

#### ACKNOWLEDGMENT

Je remercie vivement mon directeur de thèse, Processeur Daniel Etiemble, Professeur d'Université Paris Sud, pour tous ses conseils et discussions techniques.

J'exprime ma profonde reconnaissance à mon co-directeur de thèse, Processeur Omar Hammami, processeur de l'ENSTA ParisTech, pour toute la confiance qu'il m'a témoigné et toute sa disponibilité à diriger cette thèse. Je le remercie également pour les longues discussions techniques, pour les précieux conseils qu'il m'a donné, et pour tout ce qu'il m'a appris pendant cette thèse et lors de la rédaction de ce manuscrit. Je le remercie enfin de m'avoir permis d'intégrer son équipe.

Je remercie Messieurs Guy Gogniat, professeur à l'université de Bretagne Sud et Smail Niar, professeur à l'université de Valenciennes, pour le temps qu'ils ont consacré à l'examen de mes travaux et à la rédaction du rapport de thèse.

Je remercie Monsieur Alain Mérigot, Professeur à l'université Paris Sud, pour avoir accepté de présider le jury.

Je remercie, bien évidement, Xinyu Li, Zhoukun Wang, Mazen Khaddour, Muhammad Imran Taj et tous mes amis, collèges de l'ENSTA pour leur soutien pendant le moment le plus difficile.

Enfin, et sur tout, je remercie ma famille pour son soutien, sa compréhension et ses encouragement.

#### **ABSTRACT**

The Software Defined Radio (SDR) is a reconfigurable radio whose functionality is controlled by software, which greatly enhances the reusability and flexibility of waveform applications. The system update is also made easily achievable through software update instead of hardware replacement. The Software Communication Architecture (SCA), on the other hand, is an open architecture framework which specifies an Operating Environment (OE) in which waveform applications are executed. A SCA compliant SDR greatly improves the portability, reusability and interoperability of waveforms applications between different SDR implementations.

The multiprocessor system on chip (MPSoC) consisting of large, heterogeneous sets of embedded processors, reconfiguration hardware and network-on-chip (NoC) interconnection is emerging as a potential solution for the continued increase in the data processing bandwidth, as well as expenses for the manufacturing and design of nanoscale system-on-chip (SoC) in the face of continued time-to-market pressures.

We studied the challenges of efficiently deploying a SCA compliant platform on an MPSoC. We conclude that for realizing efficiently an SDR system with high data bandwidth requirement, a design flow with systematic design space exploration and optimization, and an efficient programming model are necessary. We propose a hybrid programming model combining distributed client/server model and parallel shared memory model. A design flow is proposed which also integrates a NoC topology synthesis engine for applications that are to be accelerated with parallel programming and multiple processing elements (PEs).

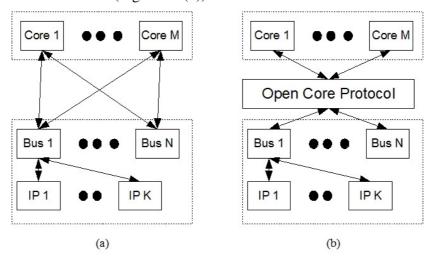

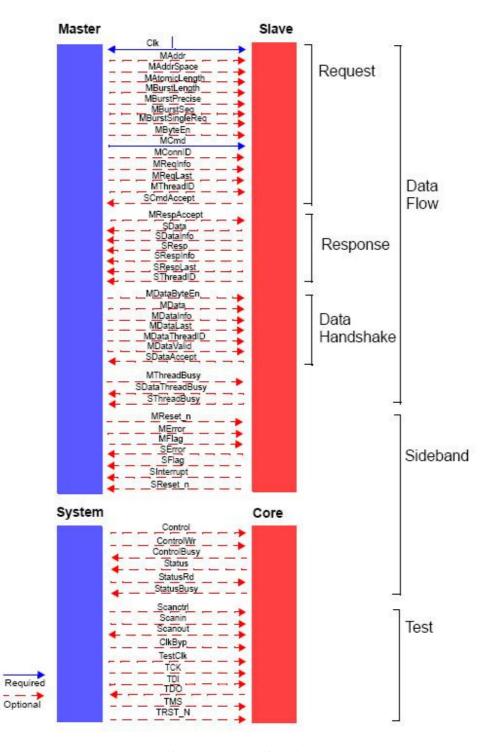

We prototyped an integrated SW/HW development environment in which a CORBA based integrated distributed system is developed which depends on the network-on-chip for protocol/packet routing, and software components are deployed with unified interface despite the underlying heterogeneous architecture and os; while the hardware components (processors, IPs, etc) are integrated through interface conforming to the Open Core Protocol (OCP).

Key works: Hybrid programming model, parallel programming, Network-on-chip, FPGA, SDR, and SCA

#### Résumé

#### 1. Motivation

Depuis la première commercialisation de systèmes mobiles cellulaires début des années 1980, l'industrie des communications sans fil a connu un développement croissant de normes de communication de la technologie première génération (1G) au standard de quatrième génération (4G). La technologie 1G a été introduite début des années 1980 et complétée début des années 1990. La technologie sans fil 1G est analogique. La technologie 2G, dont le développement a commencé fin des années 1980 et s'est terminé dans les années 1990, est souvent qualifié de « numérique », et a remplacé la technologie 1G en utilisant des signaux et des réseaux numériques. Entre la technologie 2G et la 3G, on a pu observer le déploiement intermédiaire, une technologie 2.5G, numérique mais avec des possibilités de transfert de données limitées telles que les services de SMS. Les systèmes de troisième génération 3G, développés dans les années 1990, ne se limitent plus à la seule transmission de la parole comme en 2G, mais permettent l'utilisation simultanée de la parole et de services de données à un débit plus élevé. Ainsi, les réseaux 3G permettent aux opérateurs de réseau d'offrir aux utilisateurs une gamme plus large de services plus avancés, bien qu'à des débits réseau accrus, grâce à une meilleure utilisation du spectre alloué. Successeur de la télécommunication 3G, la technologie 4ème génération (4G) fournira aux utilisateurs des services de transmission de la parole, de données, et de multimédias en temps réel, à un débit encore plus élevé. Elle offrira également une meilleure qualité de service (QoS), la sécurité et la possibilité d'interface avec des réseaux filaires constituant l'épine dorsale de l'architecture du réseau.

Afin de supporter les besoins et les contraintes des différents réseaux, de très nombreuses normes sont apparues. Les opérateurs réseaux doivent se conformer à l'ensemble de ces normes, des premières de la technologie 2G à celles attendues concernant la 3G.

Vu que chaque norme est différente et utilise même parfois des fréquences porteuses différentes, des stations ou des handsets doivent être développés, déployés et maintenus, entraînant des codes très lourds et un développement lent. Comte tenu du rythme auquel les nouvelles normes sont publiées, la conformité à ces normes pour un coût acceptable en temps

de développement et en taille de puce devient vite un un cauchemar pour toute personne impliquée dans les systèmes de communication.

Le concept de Radio Logicielle a été proposé, la première fois, par Joseph Mitola III pour faire face à une telle crise. Dans cette approche, les transformations de la forme d'onde, modulation, démodulation des signaux d'un système radio sont mises en œuvre par du logiciel plutôt que par du matériel à fonctionnalité spécifique. Les composants développés en logiciel sont ensuite implantés dans les dispositifs modernes programmables/reconfigurables, tels que les GPP, DSP, FPGA, ou ASIP. Avec de tels dispositifs, l'adaptation du système à une autre norme de communication, ou même l'évolution vers une technologie plus récente peuvent être réalisés par mise à jour du logiciel sans remplacement du matériel qui serait long et coûteux. Compte tenu des progrès de la technologie des semi-conducteurs et de la technologie sans fil fournissant un accès haut-débit à Internet fiable, les mises à jour de logiciels et la reconfiguration du système peuvent être réalisées en temps réel avec des données de configuration téléchargées via Internet. De cette façon, un dispositif unique peut être rendu compatible avec tout un ensemble de normes, par exemple, ZigBee, Bluetooth, 802.11 a/b/g/n, 3G, etc. Il est possible de réaliser le passage d'un protocole à l'autre sans dégradation de qualité de service, si la conception est rigoureuse.

La réalisation de ces fonctions concernant la radio, par logiciel, présente un avantage sous réserve de :

- 1. réutilisabilité, portabilité et d'interopérabilité des applications

- 2. La plateforme et le support de modèle de programmation permettant de maintenir la complexité de la programmation à un niveau raisonnable

La première condition est primordiale : elle est à l'origine même du concept de radio logicielle. Les avantages de la flexibilité, idée maîtresse de ce concept, ne sont effectifs que si l'on peut librement ajouter, mettre à jour ou améliorer les capacités fonctionnelles d'un système radio réalisé sous forme de modules logiciels. Idéalement, les traitements concernant les formes d'onde conçue pour une plate-forme SDR peuvent être facilement transposés à une

autre plate-forme; de même, les traitements développés par une entreprise peuvent fonctionner conjointement avec ceux d'une autre entreprise. Pour atteindre cet objectif, il faut qu'un framework ouvert et standardisé définisse des interfaces homogènes et les services auxquels une application doit se conformer.

L'architecture de communication logicielle (Software Communication Architecture, SCA), est une architecture ouverte largement acceptée pour les projets de SDR. Elle est développée par le Département de la Défense des Etats-Unis (DoD) pour la réalisation, pour un coût abordable, d'une famille de systèmes radio tactiques de haute capacité offrant des services réseaux évolutifs. La spécification SCA définit un environnement d'exploitation (Operation Environment, OE) dans lequel on exécute les applications. L'OE est constitué d'un cadre de base (Core Framework), d'un middleware minimal conforme à CORBA, et d'un système d'exploitation conforme à POSIX. La norme POSIX minimise le coût de portage des applications car elle fournit une couche d'abstraction qui rend transparentes les méthodes spécifiques de chaque système d'exploitation. CORBA permet un certain niveau de transparence et l'indépendance vis-à-vis du langage de programmation. Dans cette thèse, on s'intéresse au développement et à la programmation d'une plateforme SDR conforme à SCA.

D'autre part, beaucoup d'applications haut-débit ont besoin d'une puissance de traitement et d'une bande passante I/O supérieures à celles fournies par les systèmes traditionnels composés d'un mono-processeur accompagné de certains IPs matériels. Les nouvelles plateformes de SDR sont en général implémentées sur des plateformes multiprocesseurs système sur puce (MPSoC) exploitant ses importantes ressources de calculs avec une bonne efficacité énergique. Il existe déjà des systèmes intégrant des dizaines cœurs, des matériaux reconfigurables et le réseau sur puce. Les possibilités d'un rapide développement, déploiement et vérification des logiciels embarqués parallèles sur ces nouvelles plateformes MPSoC sont autant de points clés pour satisfaire les objectifs de performance tout en respectant les délais de mise à disposition sur le marché et le coût de développement.

Le déploiement de SDR à base de SCA sur une plateforme moderne MPSoC implique la combinaison de deux paradigmes de programmation : le modèle distribué à base de CORBA,

et le modèle parallèle utilisant la programmation SMP. La conception de SDR à base standard manque de flots de conception et d'un modèle de programmation efficace pour tirer parti de riches ressources de calcul de MPSoC de manière systématique. Dans cette thèse, nous proposons un flot de conception de SDR avec une exploration architecturale et une optimisation systématique basé sur un modèle de programmation hybride (le modèle distribué client/serveur et le modèle parallèle).

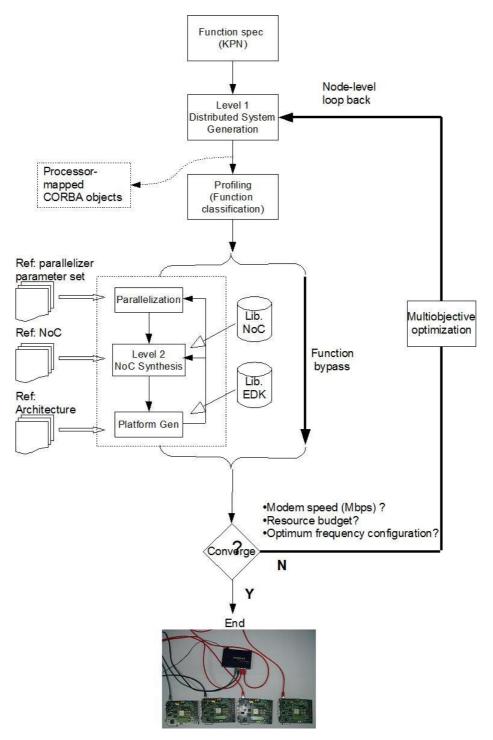

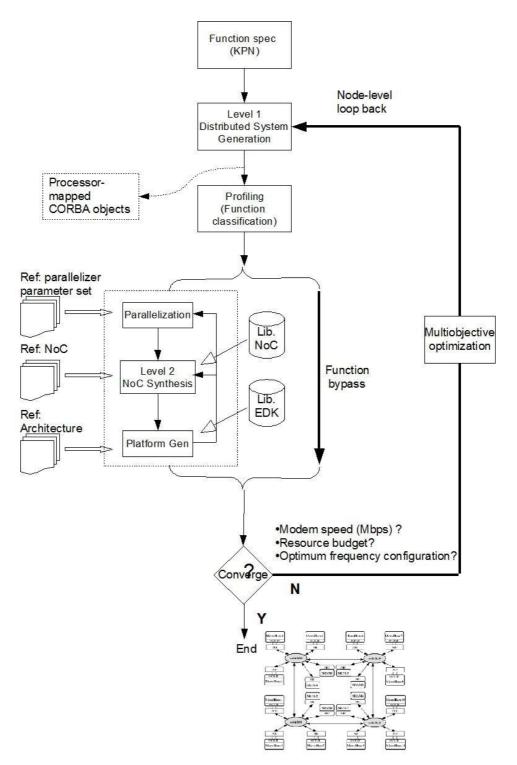

Nous nous sommes intéressés à la partie traitement de bande de base d'un système radio. Les fonctionnalités de bande de base radio sont représentées dans un réseau de processus de Kahn. Un système distribué sans contraintes de ressources est produit par un engin de générateur de système distribué d'un premier niveau. Les nœuds générés sont analysés et classés afin de déterminer ceux qui ont un important besoin en performance de calcul. Ces nœuds sont ensuite regroupés dans une sous-branche pour être parallélisés. A la sortie du flot, une voie de rétroaction globale est fournie pour permettre l'optimisation des ressources, et l'ajustement de fréquence tout en répondant aux exigences de performance du système.

#### 2. L'Etat de l'art de la radio logicielle et de la radio cognitive

Il existe des efforts sur l'implémentation de la plateforme radio logicielle ainsi que le développement d'un framework complet pour le développement et le déploiement des applications waveforms.

Le SCARI-OPEN est une implémentation de la JTRS Architecture de la communication de logiciel (SCA v2.2). Il a été certifié par le JTRS-JPO. Le projet est effectué par la Centre de Recherche de Communications (CRC) de Canada avec l'objectif de développer une référence d'implémentation (RI) afin de : 1. réduire le niveau d'ambigüité de la spécification SCA ; 2. augmenter l'interopérabilité des applications ; 3. Augmenter la compréhension de l'architecture par un exemple ; 4. accélérer l'émergence de SDRs par la disponibilité d'une implémentation ; 5. réduire le coût de développement et le délai de mise sur le marché.

L'OSSIE (Open Source SCA Implementation :: Embedded) est un core framework basé sur SCA et un outil pour le développement rapide de SDR. Il est développé à Virginia Tech et la

dernière version est la version 0.8.0 sortie en 2010. L'OSSIE contient un core framework et une suite d'outils orientés GUI (Interface Utilisateur Graphique) qui est capable de générer automatiquement les codes sources conformes à SCA et les fichiers de support permettant aux développeurs de se concentrer sur les fonctionnalités de traitement de signal.

La SDR-4000 est une plateforme émetteur-récepteur développée par Spectrum. Elle offre des COTS (Composant pris sur étagère) matériels, logiciels et services pour accélérer le développement et le déploiement des solutions pour le modem sans fil. La SDR-4000 contient deux composants principaux, l'engin de traitement modem PRO-4600 et l'émetteur-récepteur à deux canaux XMC-3321. Les deux composants ensemble constituent un modem sans fil supportant deux canaux par slot.

L'IDROMel est un projet de l'Agence Nationale de la Recherche (ANR) de France visant à définir et valider une SDR reconfigurable et une plateforme de CR. La plateforme combine les technologies les plus récentes, comme : 1. le traitement bande de base flexible ; 2. un système intégré basé sur un réseau sur puce ; 3. un support de reconfiguration partielle utilisant un FPGA ; 4. une bande RF très large de 200 MHz à 7.5 GHz ; 5. un support de 4x4 MIMO ; 6. une conception flexible de MAC pour le support de handover vertical.

Le WiNC2R développé par l'Université Rutgers est un prototype de plateforme de radio cognitive. L'Annabelle développé par l'Université de Twente, propose une architecture multiprocesseur système-sur-puce (MPSoC) pour le traitement bande de base de la radio cognitive. La SDR LSI est une solution mono-puce pour le traitement bande de base de SDR développé par Fujitsu.

Dans les chapitres suivants, nous nous intéresserons à l'aspect de traitement de bande de base de la SDR.

#### 3. L'implémentation et l'optimisation d'un système embarqué pour la SDR

Dans ce chapitre, plusieurs méthodologies de conception de multiprocesseur système sur puce (MPSoC) sont présentées. On a proposé un flot de conception de MPSoC avec l'aide d'un

paralléliseur automatique, l'outil PLuTo. PLUTO effectue des transformations source-àsource automatiques basées sur la modélisation polyédrique. Il est capable d'optimiser les séquences de boucles imbriquées pour le parallélisme à grain gros et la localité de cache simultanément. Après la transformation, un code parallèle OpenMP est généré qui peut être ensuite exécuté sur les plateformes multi-cœurs. Par contre, l'exécution du code OpenMP dépend des APIs OpenMP, du compilateur et du support runtime de l'OS qui sont rarement présents dans un système embarqué. On a donc conçu un adaptateur OpenMP vers l'environnement embarqué qui est intégré dans le flot de conception d'accélérateur.

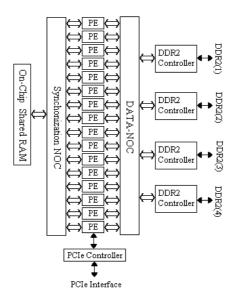

Une étude de cas est présentée dans laquelle on a programmé et évalué une plateforme multiprocesseur système sur puce à base de réseau sur puce développée par le laboratoire. Le système est composé de 16 processeurs de type Microblaze et les communications interprocesseur se font à travers un réseau sur puce avec un modèle de programmation à mémoire partagé.

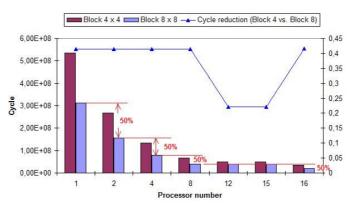

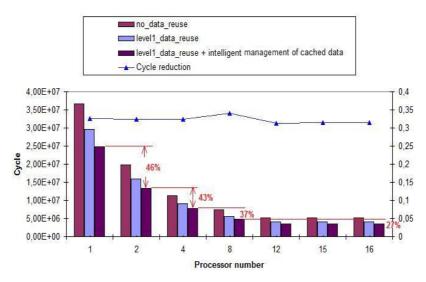

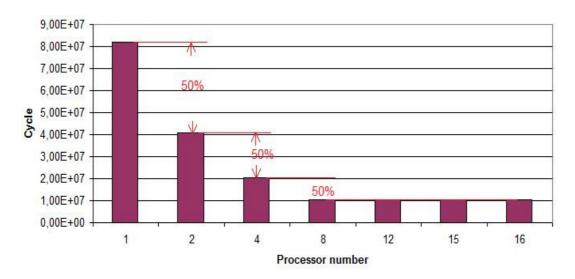

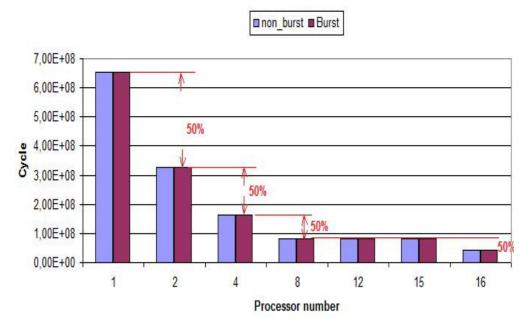

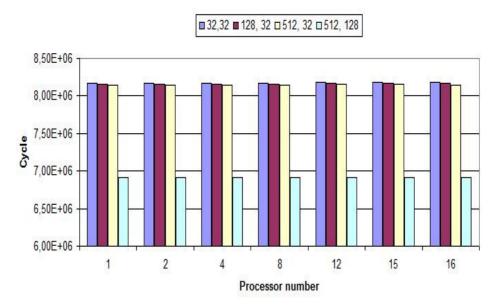

Nous avons étudié le potentiel de la parallélisation automatique sur le système multi-cœur avec 16 processeurs élémentaires (PE) interconnectés par un réseau sur puce (NoC). L'implémentation effective de matériel nous a permis d'aborder les trois sujets suivants : (1) l'efficacité du support matériel des primitives de synchronisation, (2) la performance de la parallélisation automatique, (3) les avantages de la multiprogrammation. Avec le paralléliseur PLUTO, on a fait des expériences de programmation parallèle sur la plateforme MPSoC. On a noté que plusieurs éléments clé existent qui influent sur l'efficacité de la parallélisation. Certains de ces éléments sont inhérents à l'application, tandis que d'autres dépendent de l'architecture. Une compréhension détaillée des caractéristiques aussi bien de l'application que de l'architecture est essentielle pour obtenir une performance satisfaisante. On a programmé la multiplication de matrices, Seidel, la DCT, et Jocobi 1d. La multiplication de matrices et la DCT présentent de bonnes caractéristiques pour la parallélisation et la performance évalue linéairement quand le nombre de processeurs augmente. La performance pour Seidel atteint un pallier quand le nombre de processeur dépasse 8. Jocobi 1d n'expose aucun parallélisme. Il n'y a donc aucun intérêt à essayer de paralléliser cette application.

Pour la plupart des applications, les ressources des processeurs ne peuvent pas être totalement exploitées. Nous sommes naturellement conduits à la solution multiprogrammation où les ressources processeurs sont partagées par plusieurs applications. Nous constatons que le nombre de 8 processeurs est souvent un point critique au-delà duquel l'augmentation de performance avec l'augmentation de nombre de processeurs s'arrête. Une combinaison judicieuse d'applications peut effectivement améliorer la performance globale. Une solution est de partager les ressources entre plusieurs applications. On a donc fait des expériences de multiprogrammation sur la même plateforme. Les résultats montrent une meilleure utilisation de ressources.

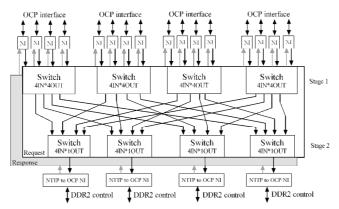

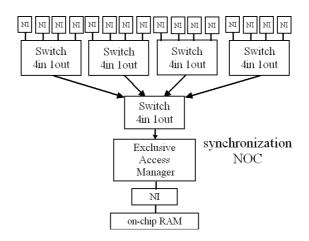

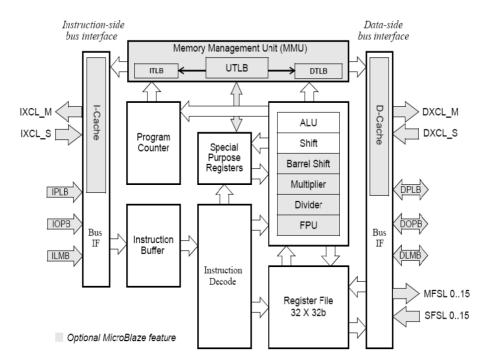

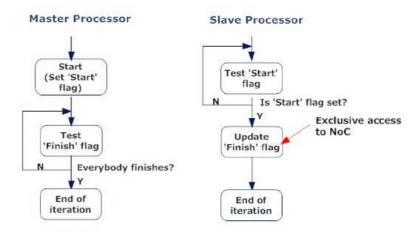

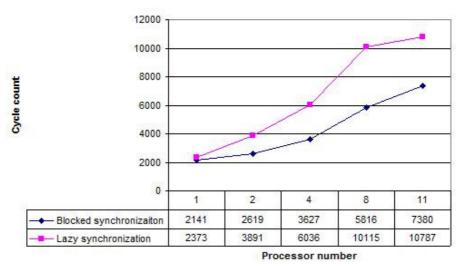

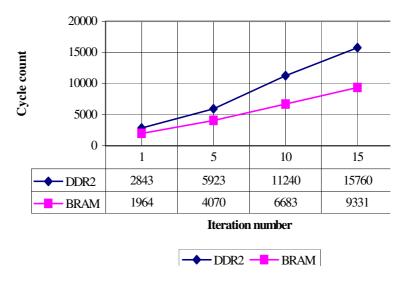

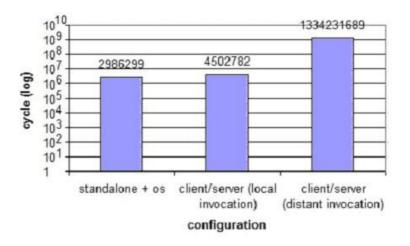

L'Unité d'Interface de Réseau (Network Interface Unit, NIU) du MPSoC en question est basée sur le Protocole Open Core (OCP). OCP est un protocole non propriétaire. Il établit un standard commun pour l'intégration des propriétés intellectuelles (IPs) à la façon « plug et play ». Le protocole OCP est basé sur le modèle maître-esclave point-à-point. Nous nous sommes intéressés à deux des mécanismes de synchronisation fournies par le protocole OCP, plus précisément : la synchronisation exclusive, et la synchronisation paresseuse. On a développé un benchmark de synchronisation de type barrière pour tester la performance des deux mécanismes sous différentes hiérarchies de mémoire ainsi que différentes types de mémoire. Les résultats montrent que la performance de la synchronisation exclusive dépasse celle de la synchronisation paresseuse de 50% quand les variables de synchronisation sont centralisés. Quand il s'agit du même mécanisme de synchronisation avec différents types de mémoire, on a constaté que lorsque la variable de synchronisation est placée dans la mémoire sur puce BRAM, la performance est meilleure que lorsqu'elle est dans la DDR.

## 4. Le mapping de middleware sur un système embarqué distribué à base de réseau

Il y a de plus en plus de systèmes qui sont composés d'une collection de composants divers interconnectés par un réseau où chaque composant exécute des fonctionnalités qui impliquent à la fois l'interaction locale et distante avec d'autres composants du système. Stimulée par l'augmentation du nombre d'applications à base de réseau, la technologie middleware est devenue de plus en plus importante. Dans un système distribué, le middleware est défini comme une couche de logiciel qui se situe entre le système d'exploitation et les applications.

Par cacher l'hétérogénéité de l'architecture, l'OS sous-jacent et le langage de programmation, le middleware facilite l'intégration d'application, améliore la portabilité des composants logiciels et l'interopérabilité des applications développées par différentes entreprises.

Dans ce chapitre, on a introduit la spécification middleware du Groupe de Management d'Objets (Objet Management Group, OMG): c'est Common Object Request Broker Architecture (CORBA) et sa version embarquée, l'eCORBA.

Il existe de nombreuses implémentations de CORBA académiques ou commerciales. On a présenté omniORB, qui est développé par le Laboratoire AT & T de Cambridge. OmniORB sera plus tard choisi comme middleware dans notre système distribué.

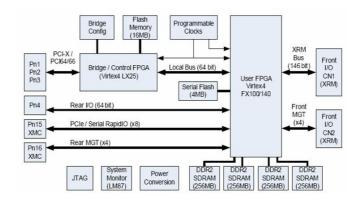

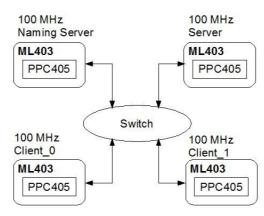

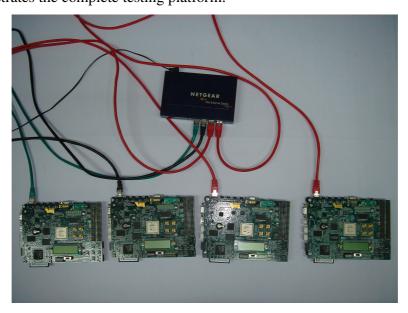

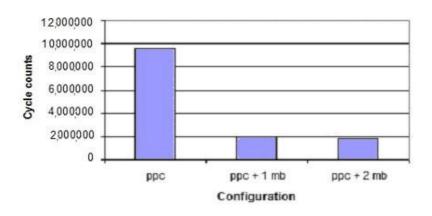

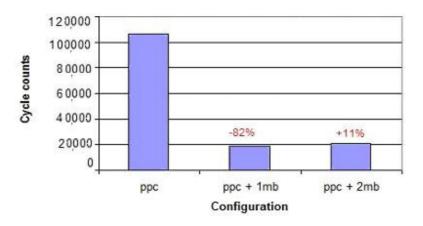

Nous avons construit un système embarqué distribué utilisant plusieurs cartes FPGA comme plateforme de preuve de concept. Les cartes sont interconnectées via un commutateur Ethernet. Chaque carte contient un système de calcul à base de processeur PowerPC405 disposant d'un système d'exploitation Linux avec une pile TCP/IP. Les applications de communications sont développées à l'aide du middleware CORBA conforme à la spécification SCA. La performance du middleware est évaluée à l'aide de micro-benchmarks d'évaluation. Les effets de l'augmentation de fréquence sur la performance globale du système sont examinés pour chaque composant du système (Client, Serveur, ou Services communs). Les résultats donnent de bonnes indications sur le domaine de fréquences qui minimise la consommation d'énergie.

A la fin de ce chapitre, on a proposé un flot de conception pour la SDR avec l'exploration architecturale systématique et l'optimisation multi-objective utilisant le modèle de programmation hybride (distribué client/serveur + parallèle).

#### 5. Le mapping de middleware sur un mono-puce multiprocesseur système

L'objectif ultime est d'intégrer l'ensemble sur une seule puce pour fournir une plateforme de SDR bande de base conforme à SCA. La plateforme hybride, basée sur un commutateur Ethernet, dont on a parlé, tout en permettant une preuve-de-concept rapide et pertinente, a ses

limites comme la bande passante du réseau et la flexibilité de configuration en raison de l'isolement des nœuds. Afin de bien tirer parti de l'interopérabilité et de la portabilité des applications à base de CORBA, la conception de plateforme SDR conforme à SCA sur une mono puce implique d'effectuer l'adaptation du mécanisme de transmission de CORBA de GIOP/IIOP à une couche de communication sur puce propriétaire. Dans notre cas, on va utiliser la bibliothèque Danube d'Arteris [65] pour l'interconnexion de plusieurs dispositifs de calcul, des mémoires, et des IPs via une interface standard, le Open Core Protocol (OCP). Le mécanisme de transport de CORBA est par défaut TCP/IP via internet. On va garder TCP/IP comme protocole de la couche transport et de la couche réseau de CORBA. Par contre, on va modifier la couche MAC en remplaçant Ethernet par OCP/NTTP. NTTP est un protocole de transport de paquet propriétaire implémenté dans les composants de Danube. Avec cet empilage de protocole, la couche de communication de CORBA peut rester largement inchangée et un driver gérant l'interface OCP doit être inclus au noyau Linux afin de traiter les interruptions générées par la couche OCP et router correctement les paquets entre les couches de protocoles. Avec cette solution mono-puce, les ressources peuvent être librement allouées aux nœuds nécessitant des calculs intensifs qui peuvent alors utiliser des dispositifs de calcul parallèles afin d'accélérer le calcul.

Le modèle de programmation distribué sur puce est inspiré de l'approche traditionnelle pour les grands systèmes. Mais il faut aussi prendre en compte les contraintes et les opportunités que permettent les SoCs. Par exemple, la taille maximale de transmission (MTU) doit être adaptée aux ressources mémoire de l'interface MAC, et la longueur maximale d'une écriture en mode burst du réseau sur puce afin de pouvoir envoyer un paquet de données de manière atomique. D'autre part, contrairement au réseau informatique, le réseau sur puce offre un meilleur taux de succès de transmission, et divers services comme le contrôle de flux, l'accusé de transmission fourni par le Network Interface Unit (NIU). Par conséquent, les services correspondants fournis par la couche transport (TCP) peuvent être économisés.

Une autre partie de la thèse porte sur la synthèse de topologie de réseau-sur-puce (PSTRP) pour la sous-branche de parallélisation du flot de conception. Le problème de la synthèse de la topologie du réseau-sur-puce peut se modéliser sous forme de programme linéaire en nombres

entiers. On a étudié deux modèles de communications, le passage de messages et la mémoire partagée. Les résultats montrent que les contraintes d'implémentation, comme la hiérarchie du réseau sur puce, doivent être prises en compte pour obtenir un résultat à la fois mathématiquement optimisé et électroniquement réalisable.

## **CONTENTS**

| Flot de C | Conception Système sur Puce pour Radio Logicielle             | i    |

|-----------|---------------------------------------------------------------|------|

| ACKNO     | WLEDGMENT                                                     | iii  |

| ABSTRA    | ACT                                                           | V    |

| Résumé.   |                                                               | vii  |

| CONTE     | NTS                                                           | xvii |

| LIST OF   | TABLES                                                        | XX   |

|           | FIGURES                                                       |      |

|           | 1                                                             |      |

| •         | ion                                                           |      |

|           |                                                               |      |

|           | 2 Software Defined Radio and Cognitive Radio State of the art |      |

| 2.1       | SDR Definition                                                | 9    |

| 2.2       | SCA Specification                                             | 10   |

| 2.3       | CR Definition and theoretical issues                          | 13   |

| 2.4       | Academic SCA based SDR (OSSIE and SCARI)                      | 14   |

| 2.5       | Commercial SCA based SDR (Spectrum Signal)                    | 15   |

| 2.6       | Other efforts in SDR implementations                          | 17   |

| 2.7       | Academic CR major projects and achievements                   | 22   |

| 2.8       | Conclusion                                                    | 23   |

| Chapter 3 | 3 Embedded System Implementation and Optimization for SDR     | 25   |

| 3.1       | MPSoC and FPGA Design Flow                                    | 25   |

| 3.2       | Optimization Based Design Flows                               | 31   |

| 3.3       | Automatic Parallelization State of the Art: The case of PluTo | 33   |

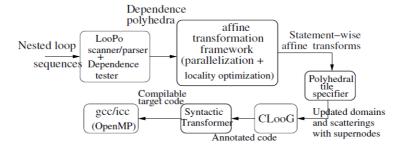

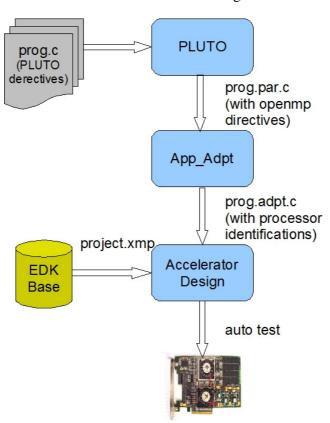

| 3.4       | Automatic parallelizer based MPSoC design flow                | 36   |

| 3.5       | Case study: A NoC based MPSoC programming and optimization    | 38   |

| 3.5.      | 1 MPSOC platform                                              | 38   |

| 3.5       | 2 OCP-IP Specification                                        | 41   |

| 3.5.3       | Synchronization with OCP-IP                                         | 44          |

|-------------|---------------------------------------------------------------------|-------------|

| 3.5.4       | Synchronization results and analysis                                | 46          |

| 3.5.5       | Experiments of automatic parallelization                            | 49          |

| 3.5.6       | Multi-programming Experiments and Analysis                          | 55          |

| 3.6 Co      | onclusion                                                           | 57          |

| Chapter 4 M | Mapping middleware on Distributed Networked Embedded Systems        | 59          |

| 4.1 C       | ORBA, e/CORBA and OmniORB                                           | 59          |

| 4.1.1       | CORBA interoperability and GIOP/IIOP                                | 62          |

| 4.1.2       | CORBA/e                                                             | 64          |

| 4.2 or      | nniORB                                                              | 65          |

| 4.3 A       | nalysis Case studies: Performance and Scalability                   | 67          |

| 4.3.1       | Distributed Embedded System Hardware Architecture                   | 67          |

| 4.3.1.1     | ML403 board                                                         | 67          |

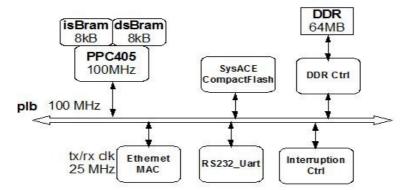

| 4.3.1.2     | Architecture of the distributed processing node based on a virtex4f | x12 FPGA    |

|             |                                                                     | 69          |

| 4.3.2       | Software architecture                                               | 70          |

| 4.3.3       | Performance Evaluation                                              | 72          |

| 4.3.3.1     | Middleware benchmarking                                             | 72          |

| 4.3.4       | Performance of the Server/Client distributed platform when increase | asing clock |

|             | frequency                                                           | 76          |

| 4.3.5       | Distributed Client-server with Multiprocessor Networked Embedde     | ed Latency  |

|             | and Bandwidth Analysis                                              | 82          |

| 4.4 H       | ybrid programming model                                             | 83          |

| 4.5 M       | Iultiobjective Optimization Based Automatic Design flow for COF     | RBA based   |

| Distribute  | ed Networked Embedded Systems                                       | 88          |

| 4.6 C       | onclusion                                                           | 89          |

| Chapter 5 M | Middleware mapping on Single Chip Multiprocessors                   | 93          |

| 5.1 St      | tate of the art of Middleware Mapping on Multi-processor Platforms  | 93          |

| 5.2 N       | etwork on Chip technology                                           | 95          |

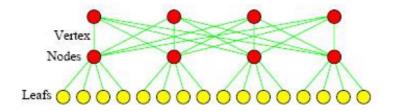

| 5.2.1       | SPIN                                                                | 96          |

| 5.2.2       | AEthereal                                                           | 96          |

| 5.2.      | 3 Nostrum96                                                                |    |

|-----------|----------------------------------------------------------------------------|----|

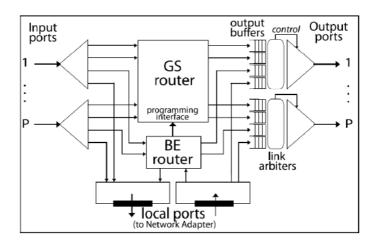

| 5.2.      | 4 MANGO97                                                                  |    |

| 5.2.      | 5 Arteris NoC technology                                                   |    |

| 5.3       | Synchronization Issues with CORBA Based designs                            |    |

| 5.4       | OCP-IP Protocol and CORBA                                                  |    |

| 5.5       | Network Interface design and low level APIs                                |    |

| 5.6       | Network-on-chip design                                                     |    |

| 5.6.      | 1 Protocol definition                                                      |    |

| 5.6.      | 2 NoC connection                                                           |    |

| 5.6.      | 3 Memory mapping                                                           |    |

| 5.7       | Single FPGA Chip NOC Based Multiprocessor Design                           |    |

| 5.8       | Performance results                                                        |    |

| 5.9       | Design Flow for Client-server with Automatic Parallelization Paradigm MPSC | )C |

|           |                                                                            |    |

| 5.9.      | 1 Network-on-chip synthesis                                                |    |

| 5.9.      | 1.1 Definition of problem in terms of graph                                |    |

| 5.9.      | 1.2 Integer linear programming                                             |    |

| 5.9.      | 1.3 Case study                                                             |    |

| 5.10      | Conclusion                                                                 |    |

| Chapter   | 6123                                                                       |    |

| Conclusi  | ion                                                                        |    |

| Referenc  | ees127                                                                     |    |

| List of m | ublications 141                                                            |    |

## LIST OF TABLES

| Table 1 Supported data rates for each wireless generation                       | 2             |

|---------------------------------------------------------------------------------|---------------|

| Table 2 Data rates for various wireless standards                               | 3             |

| Table 3 IDROMel summary                                                         | 18            |

| Table 4 WiNC2R baseband summary                                                 | 19            |

| Table 5 Annabelle baseband summary                                              | 21            |

| Table 6 SDR LSI baseband summary                                                | 22            |

| Table 7 polycc command-line options                                             | 35            |

| Table 8 OCP MCmd                                                                | 44            |

| Table 9 Matrix Multiplication (128 * 128 Block size 8 * 8) / DCT (32 * 32 Block | size 4 * 4)   |

|                                                                                 | 55            |

| Table 10 DCT (32*32 Block Size 4*4) / Seidel 128*128 Level1_Data_Reuse and      | l intelligent |

| management of cached data                                                       | 55            |

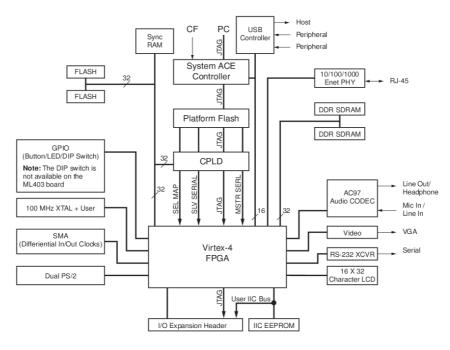

| Table 11 Principal components of the ML403 board                                | 68            |

| Table 12 Resource utilization                                                   | 70            |

| Table 13 Time of round-trip Echo function without any message                   | 73            |

| Table 14 Latency measurements for other architectures                           | 74            |

| Table 15 Throughput for 1 MB transfer in one-way invocation                     | 75            |

| Table 16 Resource utilization                                                   | 84            |

| Table 17 Resource utilization                                                   | 88            |

| Table 18 Arteris Danube transport units IPs                                     | 100           |

| Table 19 Communication layer adaptation choices                                 | 105           |

| Table 20 NTTP Global memory map                                                 | 111           |

| Table 21 Time of round-trip Echo function with zero message body                | 113           |

## LIST OF FIGURES

| Figure 1 Wireless communication standards and their data rates                    | 2          |

|-----------------------------------------------------------------------------------|------------|

| Figure 2 Single chip distributed system based on CORBA & NoC                      | 8          |

| Figure 3 Software Communication Architecture                                      | 10         |

| Figure 4 SCA Core framework in UML                                                | 12         |

| Figure 5 PRO-4600/XMC-3321 example of data flow                                   | 16         |

| Figure 6 Software Operating Environment                                           | 17         |

| Figure 7 IDROMel baseband architecture                                            | 18         |

| Figure 8 Baseband and network modules                                             | 20         |

| Figure 9 Block diagram of Annabelle base band                                     | 21         |

| Figure 10 SDR LSI architecture                                                    | 22         |

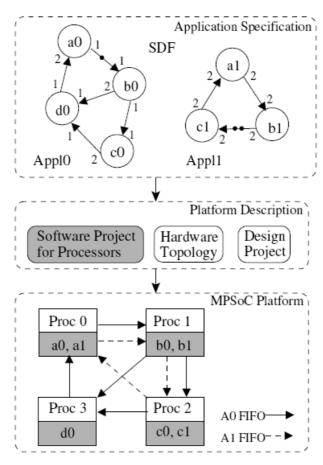

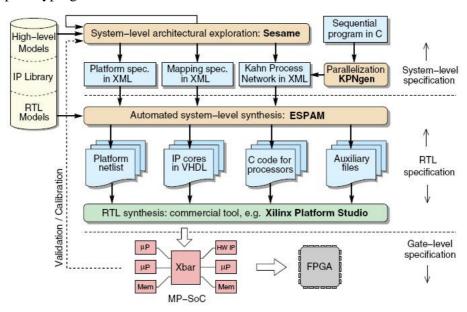

| Figure 11 Multiprocessor Synthesis Design flow [124]                              | 26         |

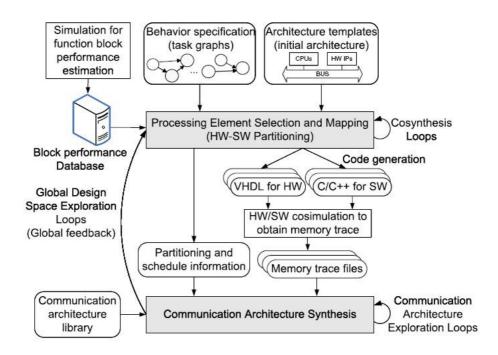

| Figure 12 Synthesis methodology for heterogeneous multiprocessors [96]            | 27         |

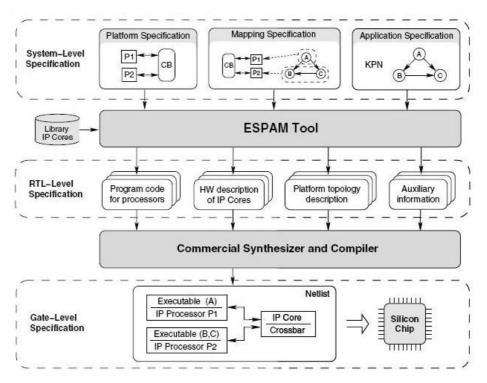

| Figure 13 ESPAM system design flow                                                | 28         |

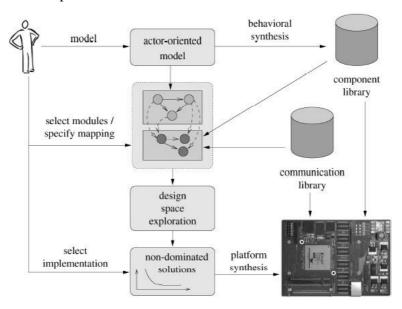

| Figure 14 ESL Design Flow using SystemCoDesigner                                  | 29         |

| Figure 15 The Daedalus system-level design framework                              | 30         |

| Figure 16 Two step design architecture exploration                                | 31         |

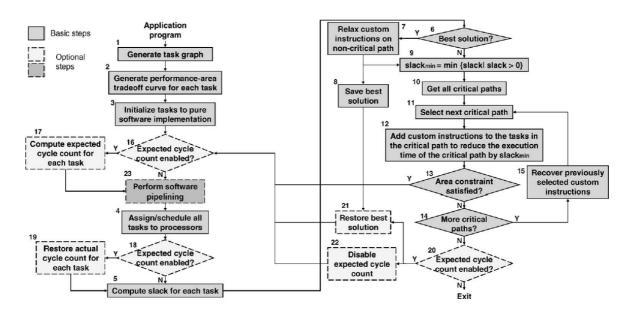

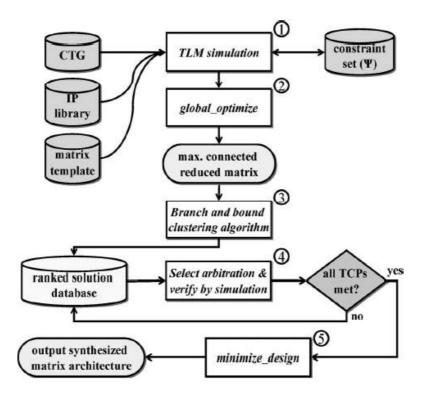

| Figure 17 BMSYN automated flow                                                    | 32         |

| Figure 18 PLuTo workflow                                                          | 34         |

| Figure 19 PLUTO transformation: (a) sequential code, (b) parallel                 | 35         |

| Figure 20 Automatic parallelizer based accelerator design flow                    | 36         |

| Figure 21 Code example of the Design flow                                         | 37         |

| Figure 22 Architecture of NoC-based multi-core                                    | 38         |

| Figure 23 Architecture of Data NoC                                                | 39         |

| Figure 24 Architecture of Synchronization NoC                                     | 40         |

| Figure 25 Block diagram of the microblaze architecture                            | 41         |

| Figure 26 System integration with a custom interface. (a) System integration with | ith an OCP |

| protocol (b)                                                                      | 42         |

| Figure 27 OCP signals                                                             | 43         |

| Figure 28 Block diagram of Alpha-Data FPGA                       | 46                                    |

|------------------------------------------------------------------|---------------------------------------|

| Figure 29 Alpha-data ADPe-XRC-4 FPGA board                       | 46                                    |

| Figure 30 Synchronization micro benchmarks                       | 47                                    |

| Figure 31 Synchronization performance: Locked vs. LL             | SC 48                                 |

| Figure 32 Synchronization performance: BRAM vs. DD               | DR249                                 |

| Figure 33 Execution results of Matrix Multiplications (1         | 28 * 128) 50                          |

| Figure 34 Execution results of Seidel 128 * 128                  | 52                                    |

| Figure 35 Execution results of DCT (32 * 32)                     | 53                                    |

| Figure 36 Execution results of DCT (64 * 64)                     | 53                                    |

| Figure 37 Execution results of Jacobi 1D                         | 54                                    |

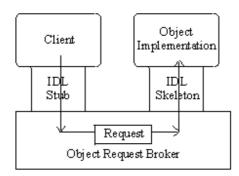

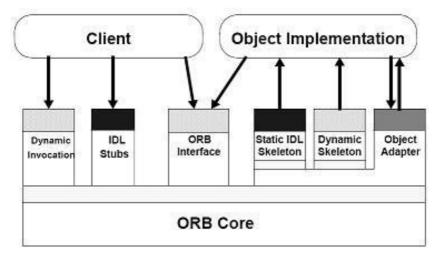

| Figure 38 A client sending a request to an object implementation | nentation[6]60                        |

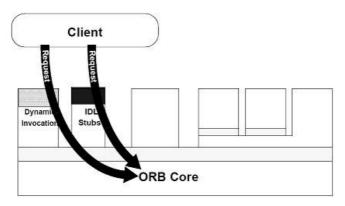

| Figure 39 The structure of Object Request Interfaces             | 61                                    |

| Figure 40 A client using the stub or dynamic invocation          | interface                             |

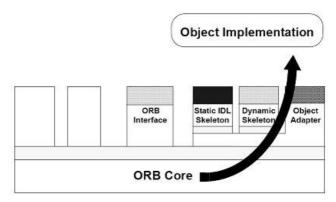

| Figure 41 An Object Implementation receiving a reques            | t 62                                  |

| Figure 42 ML403 board from Xilinx                                | 67                                    |

| Figure 43 Block diagram of the ML403 board                       | 69                                    |

| Figure 44 Block diagram of the architecture of the dist          | ributed node based on the virtex4fx12 |

| FPGA                                                             | 69                                    |

| Figure 45 Embedded distributed system based on four              | FPGA node connected by an Ethernet    |

| switch                                                           | 70                                    |

| Figure 46 Software architecture of the embedded distrib          | uted system71                         |

| Figure 47: Platform with four ML403 and a Switch                 | 71                                    |

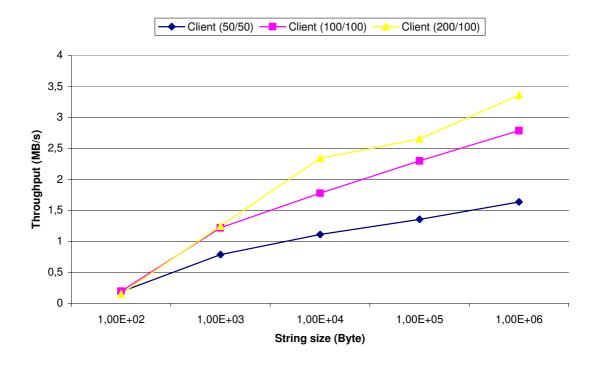

| Figure 48 Throughput for 1 MB transfer in one-way inv            | ocation74                             |

| Figure 49 Influence of Server configurations on Latency          | <i>i</i> 77                           |

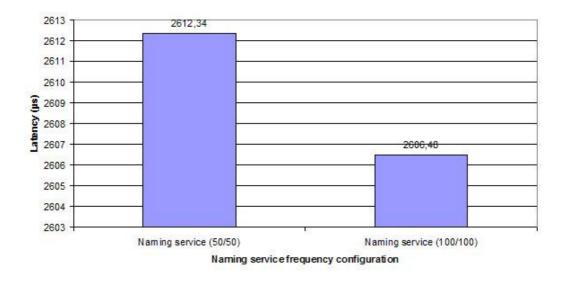

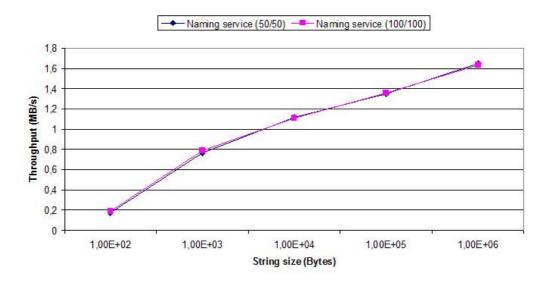

| Figure 50 Influence of Server configurations on Through          | hput78                                |

| Figure 51 Influence of Client configurations on Latency          | 79                                    |

| Figure 52 Influence of Client configurations on Through          | nput79                                |

| Figure 53 Influence of Naming service configurations o           | n Latency80                           |

| Figure 54 Influence of Naming service configurations o           | n Throughput81                        |

| Figure 55 FFT distributed computing                              |                                       |

| Figure 56 Matrix multiplication distributed computing            | 82                                    |

| Figure 57 Qam-16 distributed computing                                      | 83              |

|-----------------------------------------------------------------------------|-----------------|

| Figure 58 Block diagram of the embedded distributed system with parallel pr | rocessing units |

| (ml403 x 4)                                                                 | 84              |

| Figure 59 64-point single precision floating point FFT                      | 85              |

| Figure 60 Length-15 viterbi decoder                                         | 85              |

| Figure 61 Qam-16 modulation (16-symbol outputs)                             | 86              |

| Figure 62 Hybrid architecture with mesh-like parallel processing elements   | 87              |

| Figure 63 PPC405 + microblaze x 8                                           | 87              |

| Figure 64 Design flow based on the hybrid programming model with a          | multi-objective |

| optimization                                                                | 90              |

| Figure 65 StepNP platform                                                   | 94              |

| Figure 66 Flat tree topology                                                | 96              |

| Figure 67 MANGO router                                                      | 98              |

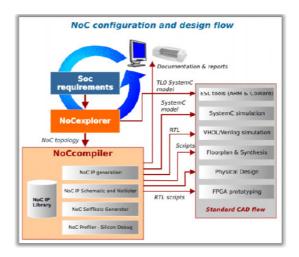

| Figure 68 NoC design flow by Arteris                                        | 99              |

| Figure 69 example of Danube IPs                                             | 99              |

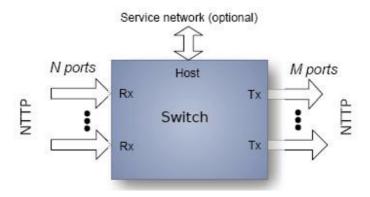

| Figure 70 Arteris Danube Switch                                             | 101             |

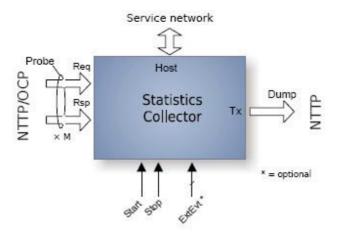

| Figure 71 Statistic collector                                               | 101             |

| Figure 72 NoCcompiler GUI                                                   | 102             |

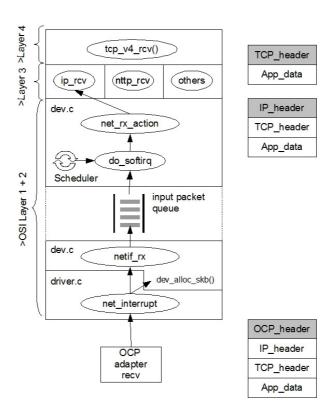

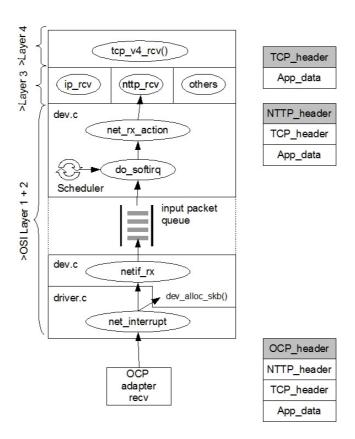

| Figure 73 TCP/IP/OCP receive sequence                                       | 106             |

| Figure 74 TCP/NTTP/OCP receive sequence                                     | 107             |

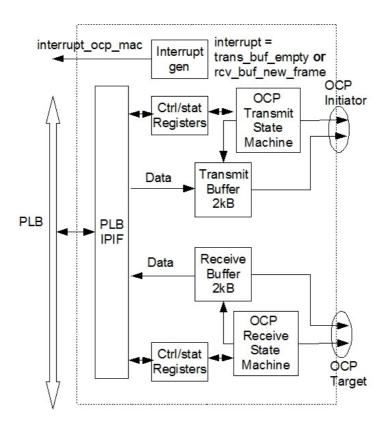

| Figure 75 Architecture of the PLB-OCP network interface                     | 108             |

| Figure 76 A two-node point-to-point connection.                             | 110             |

| Figure 77 Address translation from ocp domain to nttp domain                | 111             |

| Figure 78 Two ppc405 connected with NoC with multiplexed output             | 112             |

| Figure 79 Host machine console system                                       | 113             |

| Figure 80 Design flow based on the hybrid programming model single chip     | 114             |

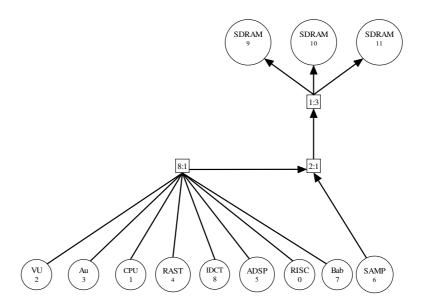

| Figure 81 MPEG4 Core graph                                                  | 119             |

| Figure 82 MPEG4 NoC topology                                                | 120             |

## Chapter 1

## Introduction

Since the first commercialization of mobile cellular systems in the early 1980's, the wireless communication industry has exhibited a rapid evolution of communication standards from first generation (1G) technology to the forth generation (4G) standard. The first-generation (1G) technology system was introduced in the early 1980s and completed in the early 1990s. 1G wireless used analog technology. The second generation (2G) technology, fielded in the late 1980s and finished in the late 1990s and often referred to as "digital", replaced the 1G technology by using digital signals and digital networks. During the transition from 2G to 3G there exists an interim deployment of 2.5G digital technology with limited data capabilities, such as short messaging services. The third-generation systems was developed in the late 1990s, which extended the voice-only digital from 2G (as enhanced), and allowed simultaneous use of speech and data services and higher data rates. Thus, 3G networks enable network operators to offer users a wider range of more advanced services while achieving greater network capacity through improved spectral efficiency. The successor to the 3G mobile telecommunication technology is the 4th generation (4G) technology that provides voice, data and streamed multimedia to users at even higher data rates, higher Quality of Service (QoS), security and interface with wire-line backbone networks.

Table 1 summarizes the advancement of wireless technology generations in terms of steady growth of data rate and new services requiring high throughput for handling Internet and multimedia content.

Table 1 Supported data rates for each wireless generation

| Wireless generation | Data rate       | Services                                |  |

|---------------------|-----------------|-----------------------------------------|--|

| 1G                  | 2.4kbps         | Voice only                              |  |

| 2G                  | 64kbps          | Voice, limited data capacity            |  |

| 3G                  | 125kbps ~ 2Mbps | Global roaming, superior voice quality, |  |

|                     |                 | M-TV, Internet                          |  |

| 4G                  | ~ 1Gbps         | Enhanced QoS, security, global          |  |

|                     |                 | roaming, wireline Internet backbone     |  |

| _                   |                 | interface                               |  |

## Data Rates (Mbits/s) 1000 PAN = Personal Area Network (10 m range) LAN = Local Area Network (100 m range) 100 MAN = Metropolitan Area Network (<3 km range) WAN = Wide Area Network (very broad coverage) 10 3.09 1 0.384 0.307 0.115 0.1 0.01 802110 WAN 02.18 0 W. Anh HOLE BUG HE STEET END

Figure 1 Wireless communication standards and their data rates

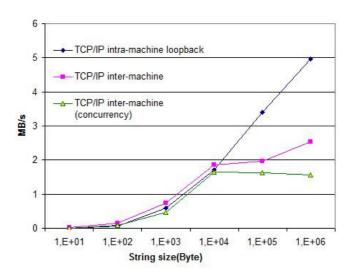

More over, in order to support the needs and constraints of various networks, a huge number of standards have appeared that operators are required to support, ranging from the early second generation to all the expected new third generation standards. Figure 1 shows the

different wireless communication standards and their corresponding data rates, while Table 2 gives more detailed information as connection, and modulation methods, for various wireless standards, including WiFi, WLAN, WiMax, WCDMA, GSM, EDGE, and ZigBee.

Table 2 Data rates for various wireless standards

| Cellular | Standard | Peak Data      | Typical Data | Connection       | Modulation |

|----------|----------|----------------|--------------|------------------|------------|

| Family   |          | Rate (kbits/s) | Rate         |                  |            |

| COM      | GSM-CSD  | 9.6/14.4       | 9.6          | Circuit Switched | GMSK       |

|          | HS-CSD   | 28.8/43.2      | 28.8         | Circuit Switched | GMSK       |

| GSM      | GPRS     | 115/171        | 50           | Packet Switched  | GMSK       |

|          | EDGE     | 385/513        | 115          | Packet Switched  | 8-PSK      |

| UMTS     | FDD      | 384/2000       | 144          | Packet Switched  | QPSK       |

| UMIS     | TDD      | 384/2000       | 144          | Packet Switched  | QPSK       |

| CDMAOne  | IS-95A   | 14.4           | 14.4         | Circuit Switched | QPSK       |

|          | IS-95B   | 65/115         | 56           | Packet Switched  | QPSK       |

| CDMA2000 | IX       | 144/307        | 130          | Packet Switched  | QPSK       |

|          | IX EV    | 2000           | N/K          | Packet Switched  | QPSK       |

| TDMA     | CSD      | 9.6            | 9.6          | Circuit Switched | π/4 QPSK   |

| PDC      | i-mode   | 9.5            | 9.6          | Packet Switched  | π/4 QPSK   |

(Data obtained from Philips 2002 & 2004 Worldwide Wireless Telecommunication Standards chart)

Since each standard is different, sometimes even using different carrier frequency, specific stations or handsets have to be developed, deployed and maintained, implying very large codes and slow developments. Considering the pace at which new standards are being released, it quickly becomes a nightmare for anybody involved in the communication industry to support them all at an acceptable cost in terms of development time and chip area.

The idea of Software Defined Radio coined by Mitola Joseph III is proposed to cope with such a crisis. In such an approach, the channel modulation waveforms in a radio system are implemented in software instead of hardware with fixed functionality. The software defined

components are deployed on modern programmable/reconfigurable devices like GPP, DSP, ASIP or FPGA. Consequently, a demand of system adaptation to different communication standards or even an update to newer generation technology can be achieved by software update instead of the tedious and time/money consuming hardware replacement. With the improvement of semiconductor technology and availability of wireless technology providing reliable and high data rate Internet access, software updates and system reconfiguration can be done in a real-time manner with configuration data downloaded form air interface. In such a way, a unique device can be made compatible with a whole set of standards, for example ZigBee, Bluetooth, 802.11a/b/g/n, 3G, etc., and handovers between different protocols can be done without degradation with careful design.

Whether the adoption of software defined radio is beneficial, however, depends on two factors:

- 1. Software reusability, portability and interoperability.

- 2. Hardware platform and programming model support to achieve the performance requirements while keeping the programming difficulty at a reasonable level.

The first factor is intrinsically important which determines the usability of the SDR idea as a whole. The benefits of flexibility, which is the main idea represented by SDR, is only achievable if one can freely add, update, or enhance functional capabilities of the radio system having been realized in form of software modules. Ideally, waveform applications designed for one SDR platform can be easily ported to another platform; waveform applications developed by one enterprise can be interoperable with the waveform applications of another company. In order to achieve this goal, an open standardized framework is necessary which provides uniform definitions of interfaces, and services an application should conform to.

The Software Communication Architecture (SCA) is a largely accepted open architecture for SDR programs. It is developed by the US Department of Defense (DoD) for the development a family of affordable, high-capacity tactical radio systems that can provide scalable, interoperable wireless mobile network services. The SCA specification defines an Operating

Environment (OE) comprising of a Core Framework, a minimum CORBA compliant middleware and a POSIX compliant operating system in which waveform applications are executed. The POSIX standard minimizes the cost of porting waveform software because it provides an abstraction layer for operating system-specific methods. CORBA provides a level of transparency and program-language independence. The developments and programming of SCA compatible SDRs are the problems treated in this thesis.

On the other hand, many of the new high-bandwidth waveforms demand processing power and I/O bandwidth that exceeds that provided by traditional single processor systems combined by certain hardware IP. New SDR platforms are most likely deployed on multi- and many- core systems (MPSoC) leveraging its rich processing resources with energy efficiency. Systems exists which incorporate dozens, hundreds or even thousands of cores. [1][2][3][4][5] Rapid development, deployment and verification of parallel embedded software in these emerging MPSOC is key issue to ensure performance requirements under strong time to market (TTM) and development cost constraints.

The deployment of SCA based SDR and the modern MPSoC platform entails the combination of two programming paradigm: CORBA based distributed model, and SMP based parallel model. Standard based SDR design lacks explicit design flow and efficient programming model for leveraging the rich processing resources that an MPSoC platform provides in a systematic manner. In this thesis, we propose a SDR design flow with systematic architecture exploration and optimization based on a hybrid programming model (distributed client/server and parallel).

We are interested in the baseband processing part of the radio system. The radio baseband functions are represented in a Kahn Process Network. A distributed system with no resource constraints is generated with a first level distributed system generation engine. The resulted nodes are profiled and classified in order to determine the ones that have a high requirement of processing performance and are passed to a sub-branch to be parallelized. At the output of the flow, a global feedback path is provided to optimize resource utilization, and frequency scaling while meeting system performance requirement.

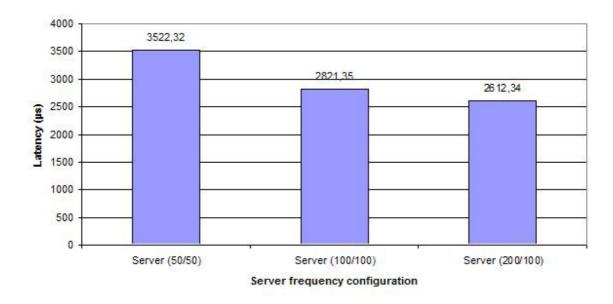

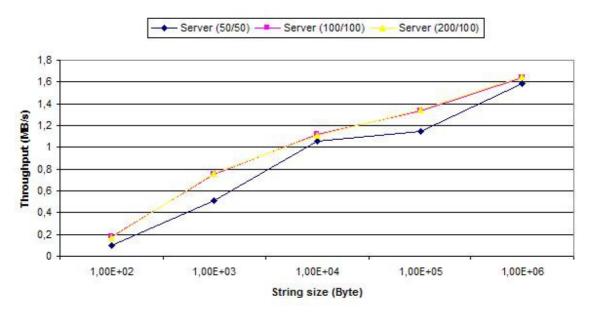

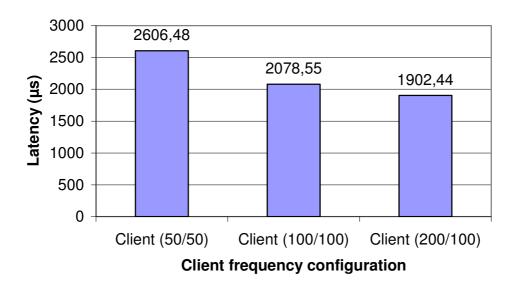

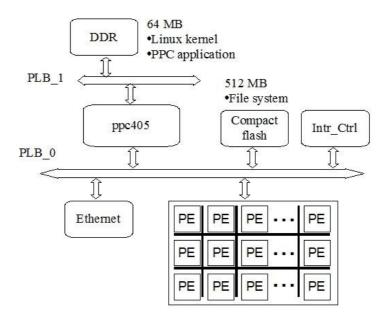

We built an embedded distributed system based on multiple FPGA cards as a proof-of-concept platform. The cards are connected via an Ethernet switch. Each card contains a PowerPC405 based computing system running Linux kernel with a TCP/IP stack. The communicating applications are realized by Common Object Request Broker Architecture (CORBA) middleware conforming to the SCA specification. The performance of the middleware is tested with micro-benchmarks. Frequency scaling effects on the overall system performance is examined on a participant-by-participant basis (Client, Server, or Common Service). The results give good clues for frequency configuration with the goal of minimizing consumption.

The parallelization sub-branch is based on an automatic parallelizer and a chain of parallel library transformation/customization tool and FPGA design tools. We studied the potential of automatic parallelization on a NoC-based 16 PE multi-core system which we designed and implemented on a single FPGA. We addressed three issues in the framework of NOC based MPSOC with actual hardware: (1) an efficient hardware support for synchronization primitives (2) the performance of automatic parallelization (3) the multiprogramming benefits.

The execution results of several parallelized code show us several key elements that influence the effectiveness of parallelization. Some of these elements are intrinsic in the application, while others are architecturally dependant. A comprehensive understanding of the characteristics of both the application and the architecture accompanied by an optimum combination of the two is necessary for a satisfying performance.

The Network Interface Unit (NIU) of the MPSoC is based on the Open Core Protocol (OCP) standard. The OCP protocol is an openly licensed, core-centric protocol intended to contemporary system level integration challenges. It provides a common standard for intellectual property (IP) core integration in a "plug and play" manner. The protocol is based on the master-slave point-to-point model. We focus on the two synchronization mechanisms provided by the protocol, namely: the Exclusive Synchronization and the Lazy

Synchronization. The results show the superiority of the blocked mechanism in the dedicated synchronization NOC with BRAM over LL-SC with BRAM or blocked with DDR in a single-lock case.

Single-application performance results show an under-exploited MPSoC platform lack of sufficient parallelizability. We are naturally led to the multiprogramming solution where processors resources are shared by multiple applications. We notice that 8 processors is usually a critical number beyond which the performance stops scaling linearly. A combination of applications and an efficient allocation of processor resources can effectively improve the overall performance.

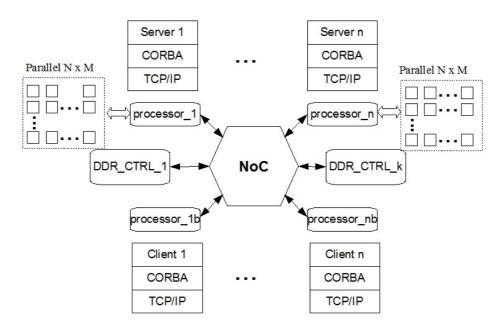

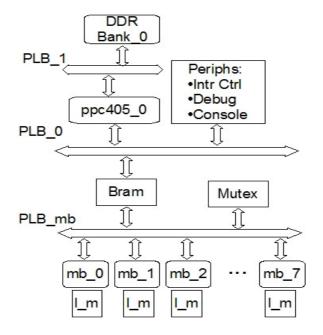

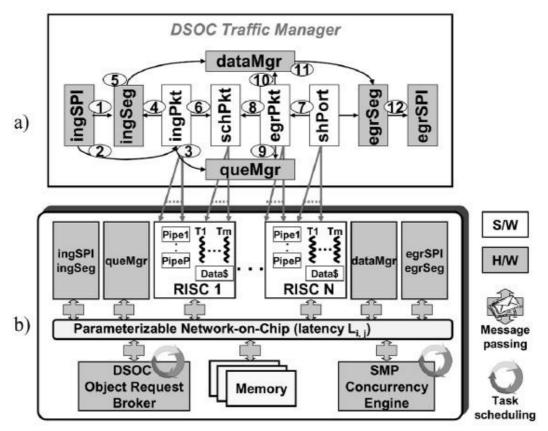

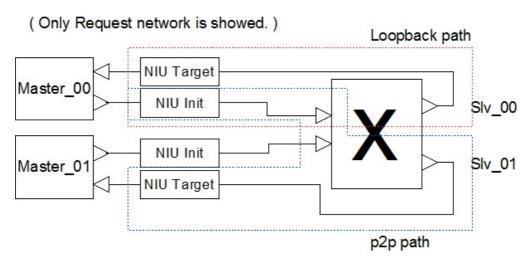

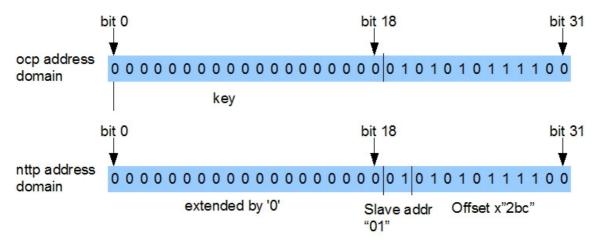

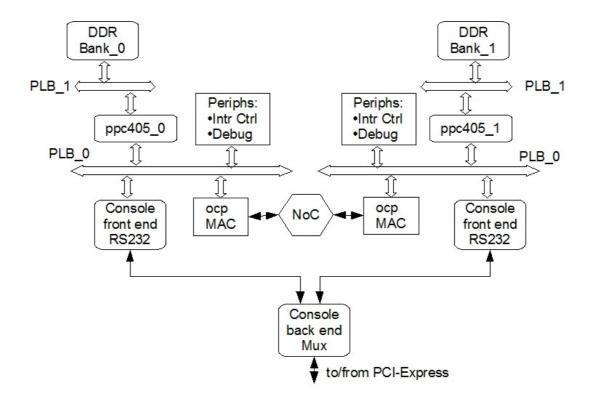

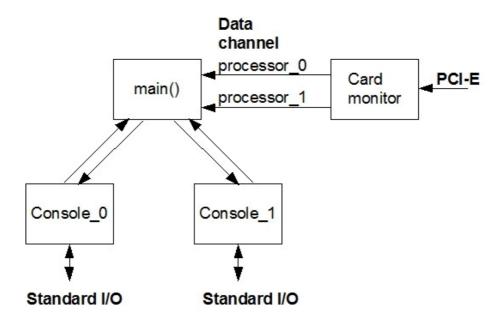

The ultimate objective is to move everything on a single chip to provide a SCA compliant single-chip SDR baseband. The Ethernet switch based hybrid platform while serving as fast and pertinent proof-of-concept has limits like network bandwidth and configuration flexibility due to the isolation of nodes. Single chip design of SCA compliant SDR platform involves efforts as the mapping of transmission mechanism of CORBA from the GIOP/IIOP to GIOP + proprietary-on-chip-communication in order to fully leverage the interoperability and portability of CORBA based applications. In our case, we will leverage the Network-on-chip (NoC) Danube library of Arteris [65] for the interconnection of multiple processing elements, memory resources and IP integration via a standard interface, the Open Core Protocol (OCP). By default, the communication mechanism of CORBA is TCP/IP. We still use TCP/IP as the transport layer and internet layer protocol of COBRA. However, we modify the MAC layer by replacing Ethernet by OCP/NTTP. NTTP is the proprietary packet transport protocol implemented in the Danube NoC. An example architecture is shown in Figure 2 that is composed of two servers and two clients whose communication is based on a version of CORBA adjusted to OCP network. With this configuration, the communication layer of CORBA can remain largely unchanged and an OCP device driver should be registered in the Linux kernel in order to handle interruptions generated by the OCP layer and route the packet properly among the protocol layers. Extra resources can be flexibly allocated to nodes in charge of processing computing-intensive algorithms by synthesizing an array of parallel processing elements to assist the computation, as is shown in upper-right corner of Figure 2.

Figure 2 Single chip distributed system based on CORBA & NoC

## Chapter 2

# Software Defined Radio and Cognitive Radio State of the art

#### 2.1 SDR Definition

The term "Software Defined Radio" was coined in 1991 by Joseph Mitola in his publication [23]. A Software Defined Radio (SDR) is a radio system, where components are implemented using software instead of hardware.

By realizing the main components in software, a SDR offers support for multiple standards, multiple bands, and seamless mode/band transitions by software update rather than hardware alternation. This greatly reduces the development and deployment cost of radio systems with the ever developing radio communications standards. SDR also have significant utility for the military area and cell phone services, both of which must serve a wide variety of changing radio protocols in real time.

There are several other important concepts that are closely related to SDR which should first be clarified, namely Digital Radio (DR), Software Radio (SR), and Cognitive Radio (CR). By the term Software Radio we refer to a transceiver whose functions are realized as programs running on a suitable processor. An SR transceiver comprises all the layers of a communication system. An ideal SR directly samples the antenna. Digital Radio is a radio system whose baseband signal processing functions are implemented on a Digital Signal Processor (DSP). A Software Defined Radio (SDR) is a presently realizable version of SR: instead of sampling directly antenna output, the received signals are sampled after a suitable

band selection filter. A Cognitive Radio (CR) [1] combines an SR with a Personal Digital Assistant (PDA) and connects its owner to Intelligent Networks (INs). [21]

## 2.2 SCA Specification

The Software Communication Architecture (SCA) [24] is an open architecture framework developed under the requirement of US Department of Defense (DoD) to maximize portability, interoperability, and configurability of the Software Defined Radio.

The SCA specifies an Operating Environment (OE) in which waveform applications are executed. In the context of SCA, a waveform is defined as the entire set of radio and/or communications functions that occur from the user input to the radio frequency output and vice versa.

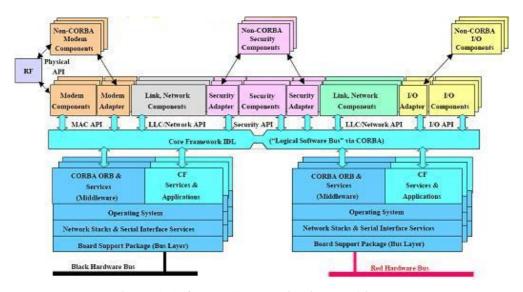

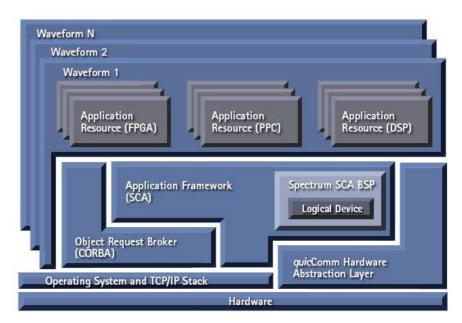

The Operating Environment is composed of a Core Framework (CF), a minimum CORBA compliant middleware and a POSIX compliant Operating System (OS). [24] The OS running the SCA must provide services and interfaces that are defined as mandatory in the Application Environment Profile (AEP) of the SCA. Figure 3 depicts the main building blocks and the hierarchy of the SCA. [25]

Figure 3 Software Communication Architecture

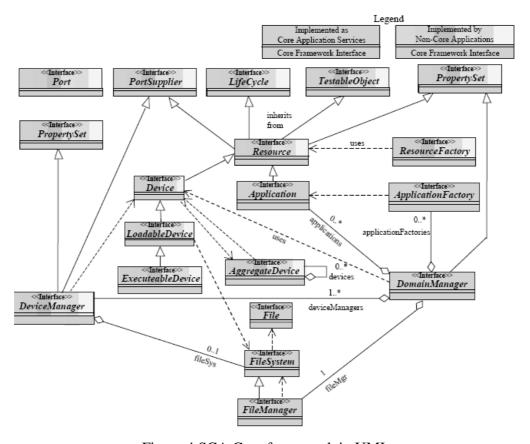

The Core Framework is a set of open application-layer interfaces and services which provide an abstraction of the underlying system software and hardware for software application designers. [21] The CF consists of four parts:

- Base Application Interfaces: provide the management and control interfaces for all system software components. The interfaces in this group are: Port, LifeCycle, TestableObject, PropertySet, PortSupplier, ResourceFactory and Resource.

- Base Device Interfaces: realize the management and control of hardware devices within the system through their software interface. The interfaces in this group are: Device, LoadableDevice, ExecutableDevice, and AggregateDevice.

- Framework Control Interfaces: control the instantiation, management, and destruction/removal of software from the system. The interfaces in this group are: Application, ApplicationFactory, DomainManager, and DeviceManager.

- Framework Services Interfaces: provide additional support functions and services such as file system management. The interfaces in this group are: File, FileSystem, and FileManager.

In Figure 4, the SCA core framework components and their interfaces are represented in UML form.

Figure 4 SCA Core framework in UML

The CF uses a Domain Profile to describe the components in the system. The software component characteristics are contained in the Software Package Descriptor (SPD), Software Component Descriptor (SCD) and Software Assembly Descriptor (SAD). The hardware device characteristics are stored in the Device Package Descriptor (DPD) and Device Configuration Descriptor (DCD). The Properties Descriptor contains information about the properties of a hardware device or software component. The Profile Descriptor contains an absolute file name for either a Device Configuration Descriptor, or a Software Package Descriptor or a Software Assembly Descriptor. Finally, the DomainManager Configuration Descriptor (DMD) contains the configuration information for the DomainManager.

The reconfiguration of radio usually concerns the installation/uninstallation of SCA applications as well as connection/disconnection of ports. These operations are accomplished by a series of function calls to the SCA Core Framework.

The following scenario depicts the steps and interfaces utilized when a client application tries to install a new application within a certain system domain. It needs to invoke the create operation provided by the ApplicationFactory interface. ApplicationFactory then refers to the Domain Profile for available devices that meet the application's memory and processor requirements, available dependant applications, and dependant libraries needed by the application. If the requirements are met, an Application instance is created and the memory and processor are allocated. The application software module is then loaded on the devices using the appropriate Device interface. Then connect the resources' ports. Finally the Application object reference in the context of CORBA Naming Service is returned.

Distributed processing is a fundamental aspect of SCA and OMG CORBA [26] is used as the middleware that provides the standardized message passing technique in a client/server model. Using CORBA allows software objects to communicate with each other through a standardized interface description language (IDL). CORBA is designed to be both language and platform independent, which simplifies the development and deployment of communication software. All CF interfaces are defined in Interface Definition Language (IDL). The CORBA handles the message marshalling and delivering.

## 2.3 CR Definition and theoretical issues

Cognitive radio is a paradigm for wireless communication in which either a network or a wireless node changes its transmission or reception parameters to communicate efficiently avoiding interference with licensed or unlicensed users. This alteration of parameters is based on the active monitoring of several factors in the external and internal radio environment, such as radio frequency spectrum, user behavior and network state. The term "Cognitive Radio (CR)" was coined by Joseph Mitola III in October 1998 to represent the integration of substantial computational intelligence – particularly machine learning, vision, and natural language processing – into software defined radio (SDR). [33] CR embeds a RF-domain intelligent agent as a radio and information access proxy for the user, making a myriad of detailed radio use decisions on behalf of the user (not necessarily of the network) to use the radio spectrum more effectively.

Although cognitive radio was initially thought of as a software-defined radio extension, most of the research work is currently focusing on Spectrum Sensing Cognitive Radio, particularly in the TV bands. The main problem of Spectrum Sensing Cognitive Radio is in designing high quality spectrum sensing devices and algorithms for exchanging spectrum sensing data between nodes. It has been shown that a simple energy detector cannot guarantee the accurate detection of signal presence, calling for more sophisticated spectrum sensing techniques and requiring information about spectrum sensing to be exchanged between nodes regularly. Increasing the number of cooperating sensing nodes decreases the probability of false detection. [144] Filling free radio frequency bands adaptively using OFDMA is a possible approach. Applications of Spectrum Sensing Cognitive Radio include emergency networks and WLAN higher throughput and transmission distance extensions.

## 2.4 Academic SCA based SDR (OSSIE and SCARI)

## 1. SCARI (CRC 2004)

The SCARI-OPEN is an implementation of the JTRS Software Communication Architecture SCAv2.2 and certified by the JTRS-JPO. The project is carried out at the Canada's Communications Research Center (CRC) and was launched in 2001 under a contract between CRC and SDR Forum to develop a reference implementation (RI) aiming at: [28]

- Reduce the level of ambiguity of the SCA specification documents

- Increase the potential for interoperability by allowing implementers to customize the RI instead of rewriting the whole architecture

- Increase understanding of the architecture through an example

- Accelerate the emergence of SDRs through the availability of an implementation

- Reduce the cost and time-to-market for SDRs

SCARI-OPEN is an open source implementation written in Java. The RI provides the mandatory components of the SCA core framework, along with support for the most used features, including Service Interfaces, Core Framework with the XML Domain Profile,

related tools to operate the radio and simple waveform applications to demonstrate the operation of radio.

The SCARI++ core framework is a new generation core framework of CRC implemented in C++. It supports an exceptional number of operating environments. Some of them are especially designed for real-time embedded systems.

#### 2. OSSIE

OSSIE, acronym for Open Source SCA Implementation::Embedded, is an open source SCA-based core framework and rapid development tool for SDR developed at Virginia Tech. [27] Its latest version 0.8.0 was released in January, 2010.

OSSIE is targeted for use in wireless communications curricula and research efforts. OSSIE includes a core framework as well as a suite of graphical user interface-oriented tools. The tools are capable of auto-generation of SCA-specific component source codes and supporting files, leaving the developer the task to specify the signal processing functionalities.

# 2.5 Commercial SCA based SDR (Spectrum Signal)

Spectrum SDR-4000 [29]

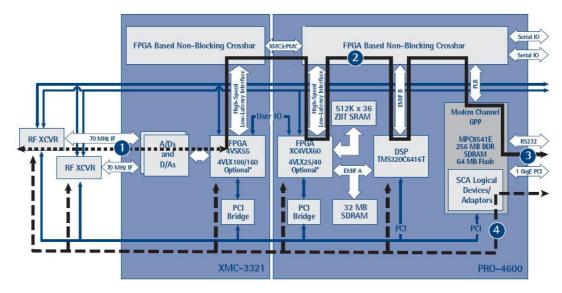

SDR-4000 is a SDR small form factor transceiver platform development by Spectrum. SDR-4000 offers the commercial off the shelf (COTS) hardware, software and services to accelerate the development and deployment of black-side wireless modem solutions for tactical military communications system. The SDR-4000 consists of two major component level products: the PRO-4600 SDR modem processing engine and the XMC-3321 dual transceiver I/O mezzanine card. The two components together provide a wireless modem that supports up to two channels per slot. Figure 5 illustrates the two components and an example of data flow.

Figure 5 PRO-4600/XMC-3321 example of data flow

The PRO-4600 component employs a combination of heterogeneous processors and FPGA: Xilinx Virtex-4 FPGA, TMS320C6416T DSP and MPC8541E GPP, which fulfills the size, weight and power-limited requirements of SDR applications.

The XMC-3321 is dual channel transceiver module optimized to operate with the PRO-4600 for SDR applications. The XMC-3321 supports 10.6, 21.4 and 70 MHz IF frequencies through the use of dual 14-bit A/D converters sampling at up to 105 MSPS and dual 14-bit D/A converters sampling at up to 300 MSPS.

Figure 6 shows the standards-based software operating environment of the SDR-4000 platform. It supports real-time operating systems such as Integrity of Green Hills or Wind River VxWorks. The SCARI Core Framework of CRC is supported by the SDR-4000, which maximizes the real-time performance of embedded platforms by providing a full implementation of all the SCA Core Framework interfaces and implementing exceptional features that minimize the boot time of an SCA system.

Figure 6 Software Operating Environment

# 2.6 Other efforts in SDR implementations

## 1. IDROMel (ANR project, France, 2009)

The project IDROMel [30] is a French National Agency for Research (ANR) project aiming at defining, developing, and validating a reconfigurable SDR and Cognitive Radio platform. The platform combines the latest technologies, such as:

- Flexible baseband processing

- Network on Chip based integration

- FPGA partial reconfiguration support

- Very wide band RF from 200 MHz to 7.5 GHz agility

- 4 X 4 MIMO support

- Flexible MAC design for vertical handover support

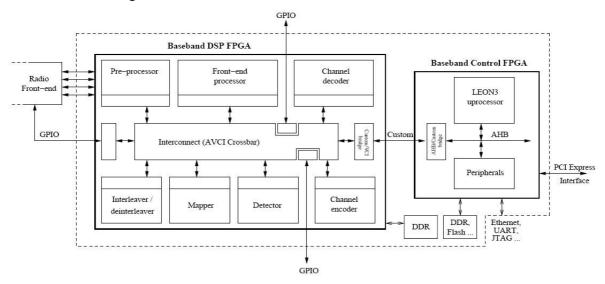

The platform permits various SDR or CR scenarios like vertical handovers in a heterogeneous network including multiple Radio Access Technologies (RATs) (with different QoS parameters, frequency bands and bandwidths). The selected RATs are UMTS and WiMax. The baseband processing part of the platform features a hierarchical heterogeneous

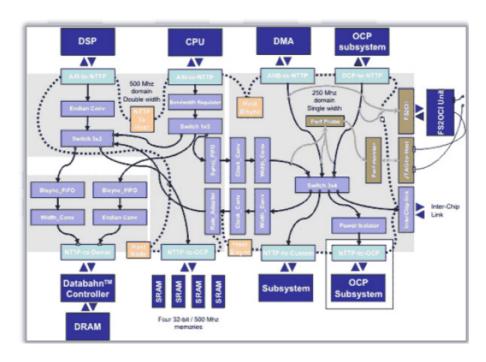

architecture. The implementation is based on two FPGAs. The first FPGA, Virtex-5LXT110 from Xilinx, implements a 32-bit microcontroller that is responsible for communications with the host-PC via a PCI-express link and for the global control of the second FPGA. The second FPGA, which is a Xilinx Vertex-5LX330 board, consists of 7 DSP blocks interconnected by a crossbar responsible for various signal processing functions and interface with the RF front end, as shown in Figure 7. The main characteristics are summarized in Table 3.

Figure 7 IDROMel baseband architecture

Table 3 IDROMel summary

| Standards  | UMTS, WiMAX                                                                         |  |  |

|------------|-------------------------------------------------------------------------------------|--|--|

| Technology | Xilinx Virtex-5110LXT control; Virtex-5                                             |  |  |

|            | 330LX processing                                                                    |  |  |

|            |                                                                                     |  |  |

| IP Core    | DFT, Generic modulator BPSK to QAM256, generic channel coder (conventional, cyclic, |  |  |

|            |                                                                                     |  |  |

|            | M-sequence), generic channel decoder                                                |  |  |

|            | (Viterbi, turbo), generic                                                           |  |  |

|            | interleaver/deinterleaver                                                           |  |  |

|            |                                                                                     |  |  |

| Processor  | 8 bit uC for each IP Core                                                           |  |  |

Partial reconfiguration of FPGA is a new feature that is capable of extending SDR perspectives by bringing the highest flexibility to the hardware level. The results show an interesting reconfiguration overhead which is as little as 700 µs/Partial Reconfiguration.

#### 2. WiNC2R (WINLAB, Rutgers University, 2008)

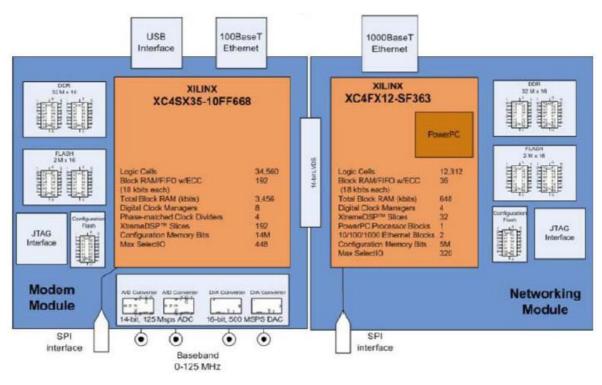

In [31], a prototype of a Cognitive Radio hardware platform – the WiNC2R is described. The platform is based on the FPGA technologies featuring rich logic resources. The flexible processing elements provide the designers a large exploration space to find the best performance/power/area tradeoff. The architecture is composed of three parts, the RF module, the baseband module and the networking module. While the RF module is mainly composed of analog circuits, the baseband module and the networking module are all implemented with FPGAs. The baseband module is implemented in Xilinx Virtex-4SX series of FPGA, which features rich DSP resources and is geared towards high-performance digital signal processing applications. The network module is implemented in the Xilinx Virtex-4FX series of FPGA, which is targeted for embedded control intensive applications. DMA engines and hardware accelerators are used to accelerate some computation-intensive PHY layer functions, like FFT, Viterbi decoding, ECC, etc, which are dynamically configurable on a per-packet basis to cover multiple standards. Figure 8 shows the baseband and network module of the WiNC2R while Table 4 lists the main baseband characteristics.

Table 4 WiNC2R baseband summary

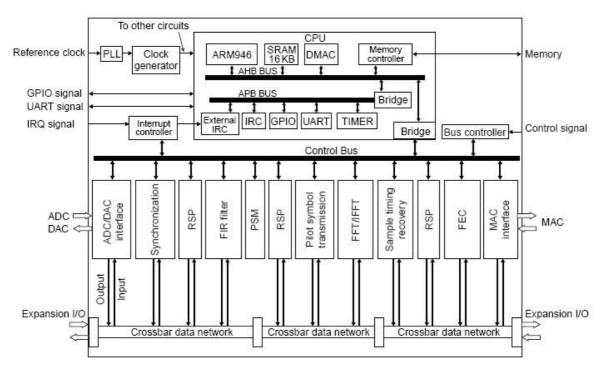

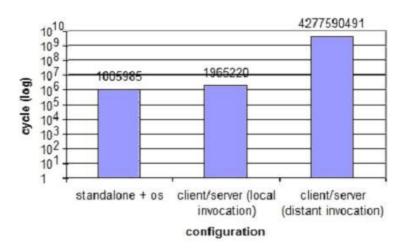

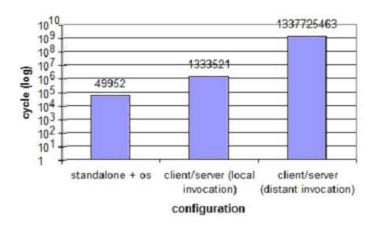

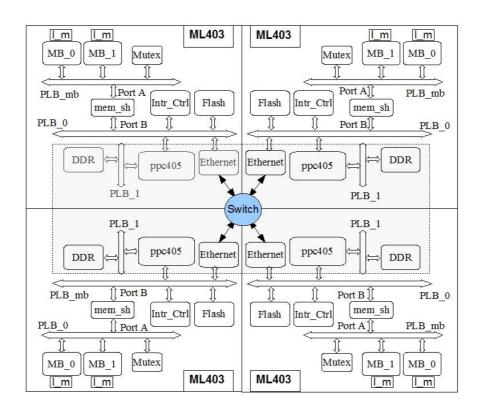

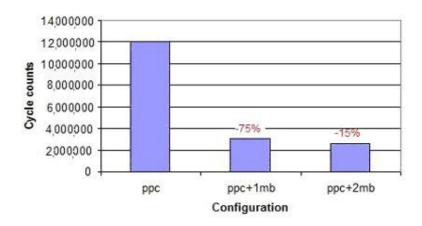

| Standard   | OFDM, QPSK/DSSS                           |  |  |